Advantages

Improved Light-Load Efficiency

Virtually eliminates hard-switching losses upon resuming burst mode operation by achieving ZVS. Improves overall system efficiency through an approximate 17% reduction in total device losses.

System Miniaturization, Weight Reduction, and Cost Reduction

Reduced power loss suppresses heat generation. Enables downsizing of cooling systems, realizing smaller, lighter, and lower-cost equipment.

High Reliability and Flexible High-Efficiency Design

Soft switching reduces stress on semiconductor devices, ensuring system longevity. Enables greater design freedom, allowing the use of large-area (low on-resistance) devices with high parasitic capacitance.

Background and Technology

In many advanced fields, such as EV charging processes and grid stabilization via SSTs, operation at light loads is common. “Burst mode,” used to improve light-load efficiency, suffers from a fundamental problem: it causes “hard switching” (turning on switches while high voltage is applied) when resuming operation, leading to significant losses and device stress.

This technology solves this problem by turning parasitic capacitance—traditionally a source of loss—into an advantage, by precisely controlling the timing of the natural “LC resonance” that occurs between it and the circuit’s inductance.

At the end of the idle period, the technology predicts the exact moment the device voltage reaches its valley (near zero) due to this LC resonance and turns the switch on at that instant. This ensures ideal ZVS upon resuming operation.

Data

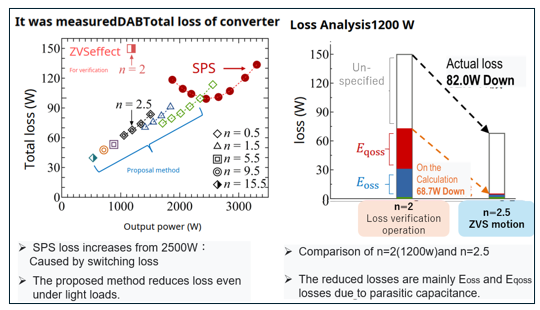

- Total Loss Comparison

Conventional SPS control (black line) shows an increase in losses in the light-load region below 1500W. In contrast, the proposed method (red line) shows a steady decrease in losses as output power drops.

- Loss Analysis

At 1200W output, applying this technology (n=2.5) dramatically reduces parasitic capacitance-related losses (Eoss, Eqoss) caused by hard switching. Total device losses were reduced from 82.0W to 67.8W, an approximate 17% reduction.

|

Expectations

This technology is expected to contribute to performance improvements in key products supporting a decarbonized society, such as EV on-board chargers (OBCs), V2G/V2H systems, Solid-State Transformers (SSTs), and Energy Storage Systems (ESS).

The core control algorithm is complete, and its effectiveness has been experimentally verified. We are seeking flexible partnerships, such as joint research and development to optimally implement this technology into your products, or technology licensing of the core IP.

Patent

JP 2025-3188

Researcher

Takanori Isobe (Associate Professor, Faculty of Pure and Applied Sciences, University of Tsukuba)

Project ID:DD-04903a